- RS Best.-Nr.:

- 865-1439

- Herst. Teile-Nr.:

- Si53119-EK

- Marke:

- Skyworks Solutions Inc

Nicht mehr im Sortiment

- RS Best.-Nr.:

- 865-1439

- Herst. Teile-Nr.:

- Si53119-EK

- Marke:

- Skyworks Solutions Inc

Mehr Infos und technische Dokumente

Rechtliche Anforderungen

Produktdetails

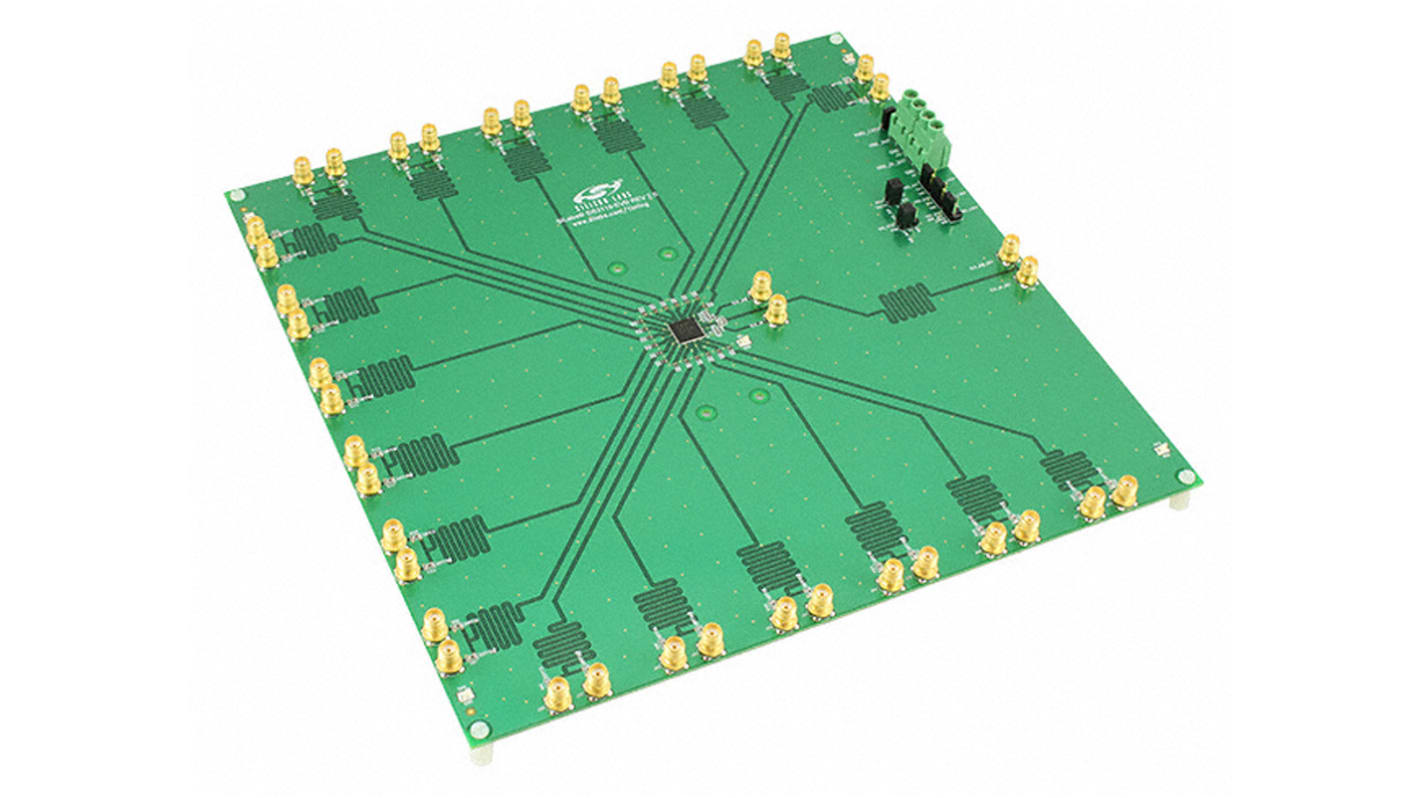

Evaluierungsplatine für Si53119, PCIe-Taktpuffer mit 19 Ausgängen, Silicon Laboratories

Der Si53119-EK von Silicon Laboratories ist ein PCIe-Taktungs- und Entwicklungskit, das einen hohen Gütegrad pro Watt beim Takten von Anwendungen bietet, welcher zur Erfüllung der PCI Express®-Standards der 1., 2. und 3. Generation erforderlich ist. Diese Taktgeneratoren und -puffer verbrauchen zweimal weniger Energie und können PCI-Express-Jitter-Spezifikationen bis zu einer Spanne von 50 % bieten. In PCIe-Taktgeneratoren und -puffern Si53119-EK von Silicon Labs sind Abschlusswiderstände vollständig integriert; dabei werden BOM-Kosten, erforderlicher Platinenplatz und Komplexität des Designs reduziert.

Si53119 ist ein energiesparender HCSL-Differenzial-Taktpuffer mit 19 Ausgängen, der alle Anforderungen der Intel-DB1200ZL-Spezifikation erfüllt.

Si53119 ist ein energiesparender HCSL-Differenzial-Taktpuffer mit 19 Ausgängen, der alle Anforderungen der Intel-DB1200ZL-Spezifikation erfüllt.

Neunzehn Ausgänge mit 0,7 V, Energiesparversion, Gegentakt-HCSL, PCIe-Standard der 3. Generation

PLL-Betrieb mit 100 MHz /133 MHz, unterstützt PCIe und QPI

PLL-Bandbreiten-SW-SMBus-Programmierung überschreibt den Latch-Wert vom HW-Stift

9 auswählbare SMBus-Adressen

SMBus-Adresse ist konfigurierbar, um mehrere Puffer in einem einzigen Steuerungsnetzwerk mit 3,3-V-Versorgungsspannungsbetrieb zu ermöglichen

Separate VDDIO für Ausgänge

PLL oder Bypass-Modus

Tolerierbare Frequenzspreizung

E/A-Versorgungsspannung von 1,05 V bis 3,3 V

50-ps-Ausgang-zu-Ausgang-Laufzeitversatz

50-ps-Zyklus-zu-Zyklus-Jitter (PLL-Modus)

Niedriger Phasenjitter (Intel® QPI, PCIe-Gen-1-/Gen-2-/Gen-3-konform)

100-PS-Eingang-zu-Ausgang-Verzögerung

Erweiterter Temperaturbereich: –40 bis +85 °C

72-poliges QFN

PLL-Betrieb mit 100 MHz /133 MHz, unterstützt PCIe und QPI

PLL-Bandbreiten-SW-SMBus-Programmierung überschreibt den Latch-Wert vom HW-Stift

9 auswählbare SMBus-Adressen

SMBus-Adresse ist konfigurierbar, um mehrere Puffer in einem einzigen Steuerungsnetzwerk mit 3,3-V-Versorgungsspannungsbetrieb zu ermöglichen

Separate VDDIO für Ausgänge

PLL oder Bypass-Modus

Tolerierbare Frequenzspreizung

E/A-Versorgungsspannung von 1,05 V bis 3,3 V

50-ps-Ausgang-zu-Ausgang-Laufzeitversatz

50-ps-Zyklus-zu-Zyklus-Jitter (PLL-Modus)

Niedriger Phasenjitter (Intel® QPI, PCIe-Gen-1-/Gen-2-/Gen-3-konform)

100-PS-Eingang-zu-Ausgang-Verzögerung

Erweiterter Temperaturbereich: –40 bis +85 °C

72-poliges QFN

Technische Daten

Eigenschaft | Wert |

|---|---|

| Takt-/Zeitgeberfunktion | Taktpuffer |

| Kit-Klassifizierung | Evaluierungsplatine |

| Vorgestelltes Gerät | Si53119 |

- RS Best.-Nr.:

- 865-1439

- Herst. Teile-Nr.:

- Si53119-EK

- Marke:

- Skyworks Solutions Inc

Verwandte Produkte

- Skyworks Solutions Inc Si5XX-PROG-EVB Evaluation Kit Evaluierungsplatine

- Skyworks Solutions Inc Si5356-EVB Evaluation Kit Evaluierungsplatine

- Skyworks Solutions Inc Si535x-TMSTK Evaluation Kit Development...

- Skyworks Solutions Inc Si5338-EVB Evaluation Kit Evaluierungsplatine

- Skyworks Solutions Inc Si5332-6EX-EVB Evaluation Kit...

- Skyworks Solutions Inc Si5338/56-PROG-EVB Evaluation Kit Programmiergerät

- Skyworks Solutions Inc Si5317-EVB Evaluation Kit Evaluierungsplatine

- Skyworks Solutions Inc Si535x-B20QFN-EVB Evaluation Kit Evaluierungsplatine