- Home

- >

- InfoZone

- >

- Electronics

- >

- Die Red-Pitaya-Plattform: Flexible und preiswerte Instrumente für jedermann

Die Red-Pitaya-Plattform: Flexible und preiswerte Instrumente für jedermann

Red Pitaya ist eine bahnbrechende Open-Source Single-Board Instrumenten- und Regelplattform mit dem Potenzial, viele verschiedene Labor- und Feldinstrumente zu einem Bruchteil der Kosten separater Geräte zu ersetzen.

Ursprünglich lieferten Prüf- und Messgeräte wie Oszilloskope und Signalgeneratoren eine feststehende Funktion und eine begrenzte Reihe an Optionen. Inzwischen haben die Hersteller dieser Prüf- und Messgeräte jedoch DSPs für ein breit gefächertes Angebot an Funktionen für ganz bestimmte Anwendungen integriert. Die Möglichkeit, diese Geräte zu programmieren und die endgültigen Funktionen festzulegen, war früher stets den Herstellern vorbehalten; und auch mit einem breiteren Angebot an Funktionen bieten die meisten Geräte heute noch immer nicht die präzisen Funktionen, die bestimmte Projekte verlangen. Dies ist insbesondere bei Wissenschaftlern an Instituten und Universitäten der Fall, die komplexe Systeme auf der Basis wesentlich kleinerer Subsysteme erschaffen, einschließlich verschiedener Instrumente. Hierbei sind oftmals Instrumente mit deutlich höheren Auflösungen als von den jeweiligen Herstellern vorgesehen zu verwenden. Probleme mit der Integration von Geräten können insbesondere bei Systemen aus zwei oder mehr Instrumenten-Subsystemen auftreten, die äußerst schnelle Rückmeldungen mit sehr geringem Jitter erfordern. Oftmals sind auch die Schnittstellen zu den jeweiligen Geräten nicht in der Lage, die Gesamtleistung des Systems zu unterstützen.

Red Pitaya

Die neue Initiative Red Pitaya knöpft sich diese Problematiken vor und gestaltet es sehr einfach, Instrumente der verschiedensten Ausführungen mit Hilfe einer einzelnen Plattform und einer Open-Source-Entwicklungsumgebung sehr preiswert zu entwickeln. Red Pitaya wurde ursprünglich über ein Kickstarter-Förderprojekt ins Leben gerufen und ist eine programmierbare und vom Anwender einstellbare Open-Source-Signalverarbeitungsplattform, die auf Xilinx Zynq®-7010 SoC (System-on-Chip) basierende Hardware mit einer Open-Source-Online-Sammlung an Geräte- und Instrumenten-Anwendungen kombiniert.

Das Zynq SoC verknüpft einen Dual-Core ARM® Cortex™-A9 Prozessor mit einer breiten Auswahl an Peripherie-Geräten und einer programmierbaren FPGA-Logik der Xilinx-7-Reihe und bietet zugleich die Grundlage für eine Vielzahl verschiedenster Instrumente, die auf Software-Apps aus der Sammlung einer Entwickler-Community bekannt als Bazaar Cloud Marketplace basieren. Darüber hinaus enthält die Sammlung Red Pitaya Backyard zahlreiche Open-Source-Entwicklungscodes und Tools zur Entwicklung verschiedenster Anwendungen, sowie die Programme Spark Center und DesignSpark, mit deren Hilfe Entwickler sich über Ideen und Vorschläge zu neuen Red-Pitaya-Anwendungen und Hardware-Erweiterungsmodulen austauschen können. Die CPU läuft auf einem Linux-Betriebssystem und unterstützt Standard-Peripheriegeräte, darunter Ethernet, USB OTG, Micro-SD-Speicher und serielle USB-Konsolen. Red Pitaya kann über verschiedenste Software-Schnittstellen, darunter HDL, C/C++ und Skriptsprachen, auf unterschiedlichen Stufen programmiert werden. Zudem bieten HTML-basierte Schnittstellen Zugang zu den Funktionen von Red Pitaya in den meisten Web-Browsern von einem Tablet, Smartphone oder PC aus.

Hardware

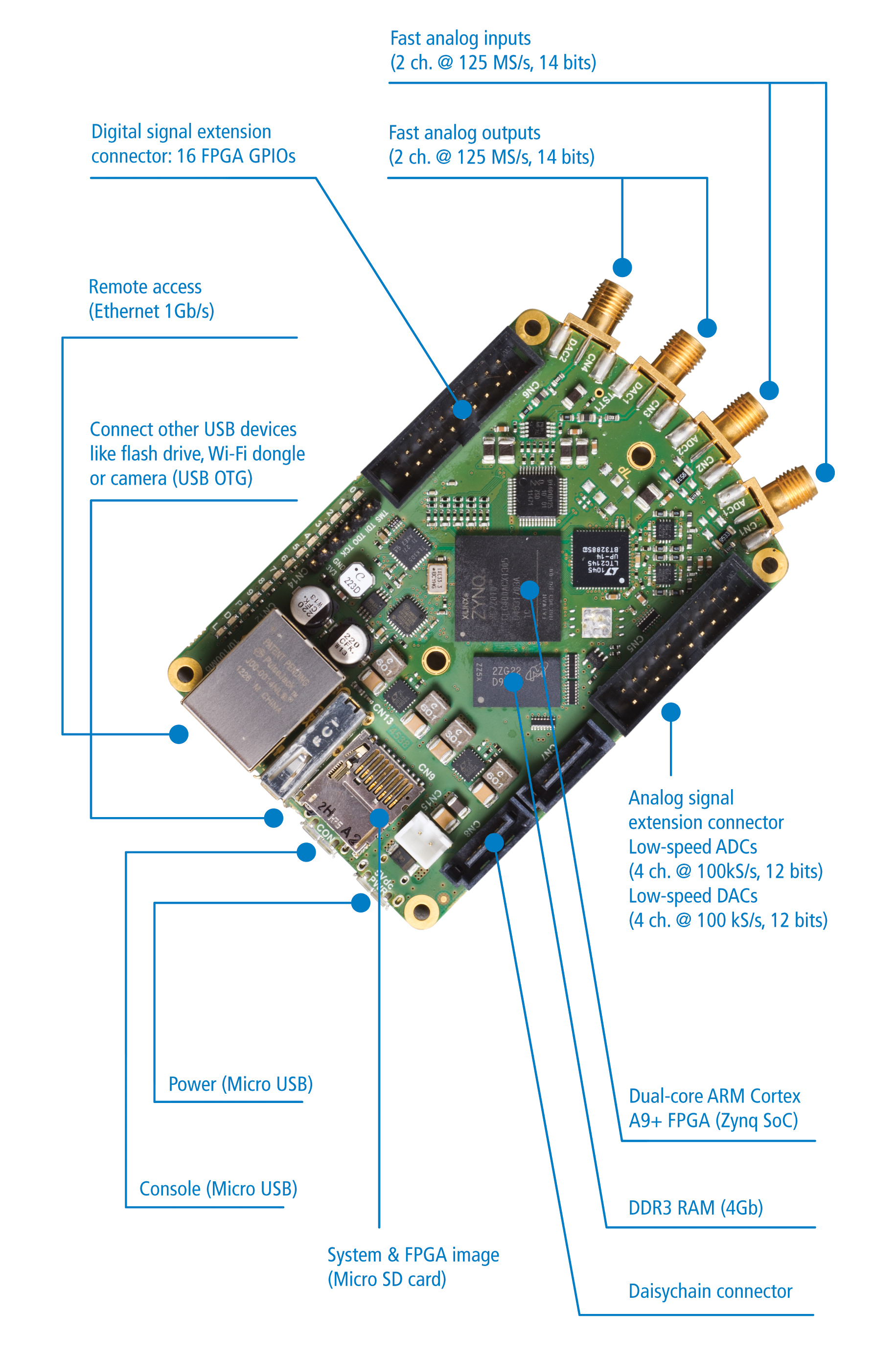

Neben dem Zynq SoC verfügt die Hardware-Plattform über zwei schnelle 125-Msample/s-Analog-Eingänge mit einer Auflösung von 14 Bit und ADCs von Linear Technology; sowie zwei schnelle 14-Bit-125-Msample/s-Analog-Ausgänge; vier 12-Bit-100ksample/s Analog-Eingänge; vier 12-Bit-100ksample/s-Analog-Ausgänge; einen USB-Anschluss und einen Ethernet-Anschluss. Die Plattform verfügt darüber hinaus über zahlreiche Erweiterungsstecker für verschiedene Hardware-Erweiterungsmodule, mit denen analoge oder digitale Anschlüsse oder ähnliche Funktionen hinzugefügt werden können. Zudem ist eine dezentrale Prozessbearbeitung möglich, wenn mehrere Red-Pitaya-Module über schnelle serielle Steckverbinder miteinander verkettet sind. Somit können skalierbare komplexe Systeme erstellt werden, bei denen zahlreiche Ein- und Ausgänge hinzugefügt werden können. Die Funktionen der Plattform werden in Abbildung 1 dargestellt.

Abbildung 1 – Die Red-Pitaya-Instrumenten-Plattform

Dabei ist ein erstes Set aus fünf Open-Source-Anwendungen erhältlich (abzuspeichern auf der On-Board-Micro-SD-Karte), die den Einsatz folgender Komponenten ermöglichen: ein digitales 14-Bit-125-Msample/s-Abtast-Oszilloskop mit zwei Kanälen; ein 60-MHz-Spektrumanalysator mit einer Wasserfall-Diagramm-Anzeige und zwei Kanälen; ein 125-MHz-ARB (Arbitrary Waveform Generator) mit zwei Kanälen; ein 60-MHz-Frequenzganganalysator mit zwei Kanälen; und ein PID-Regler (proportional, integral, derivativ) mit zwei Kanälen.

Die Funktionen zur Signalerfassung und Signalerzeugung mit 125-Msample/s und zwei Kanälen können mit der FPGA-basierten DSP-Verarbeitung zur Bildung von Hard-Real-Time-Feedback-Loops kombiniert werden. Das System verfügt zudem über zahlreiche langsamere 100-kHz-E/A-Kanäle sowie über verschiedene digitale E/As.

Architektur

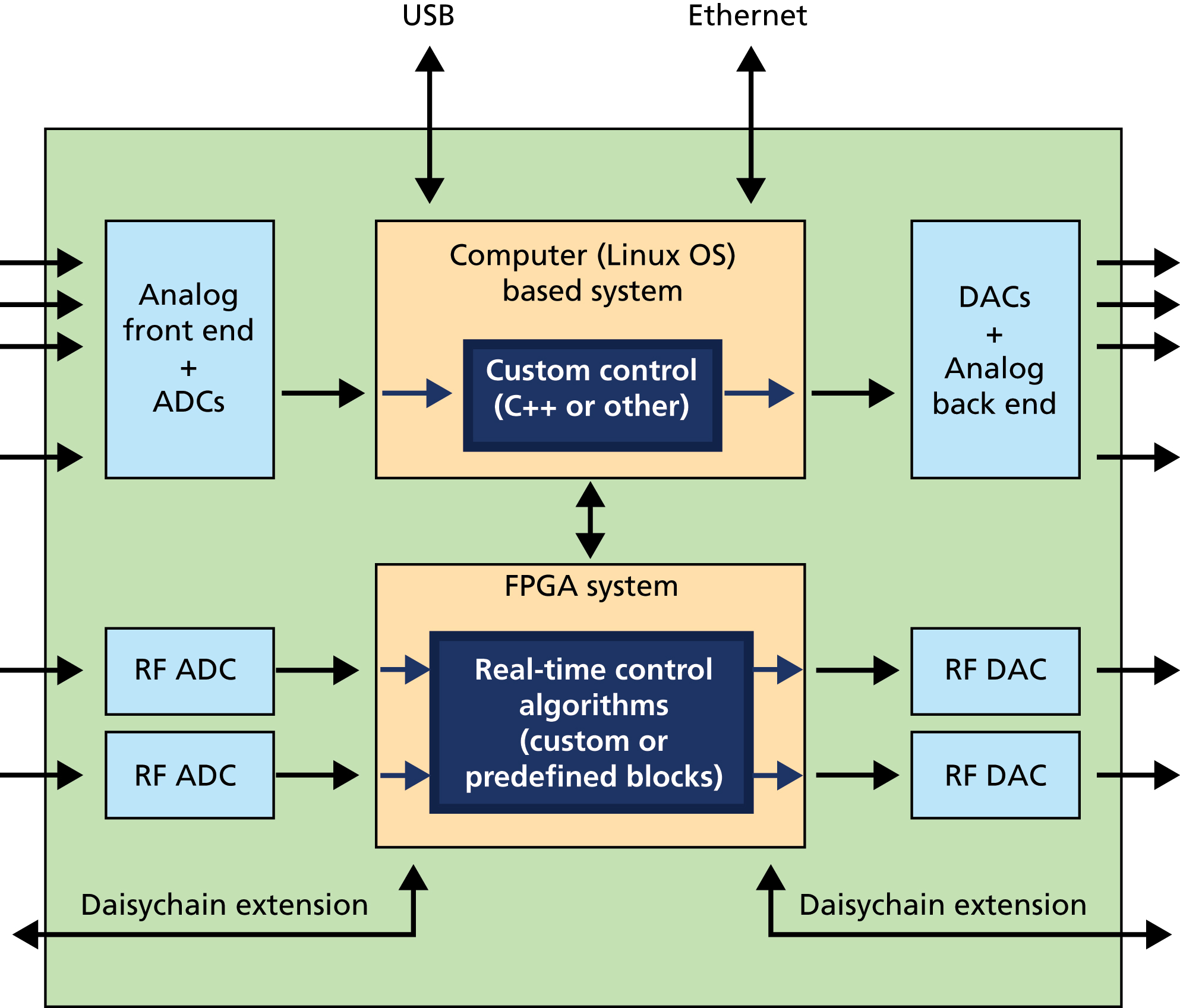

In Abbildung 2 ist die Systemarchitektur des Signalverarbeitungssystems Red Pitaya mit zahlreichen analogen und digitalen

Ein- und Ausgängen dargestellt.

Abbildung 2 – Red-Pitaya-Systemarchitektur

Die Plattform folgt dem grundlegenden Aufbau moderner Signalverarbeitungssysteme, wobei alle spezifischen Teile des Verarbeitungs- und Messsystems in der digitalen Domain zusammengefasst sind. Dieser Aufbau realisiert die Analog-Front-End- und die Back-End-Elektronik so einfach und allgemein wie nur möglich. Dabei werden die Signale mit schnellen ADCs so früh wie möglich abgetastet und so spät wie möglich zu den DACs geleitet. Die besonders digitale Architektur der Plattform erlaubt die Individualisierung der Hardware, sodass zahlreiche Vorgänge in verschiedenen Anwendungen durchgeführt werden können. Eingeschränkt werden die Möglichkeiten lediglich von der Bandbreite der analogen Front- und Back-End-Elektronik und der Rechenleistung des Prozessors und der FPGA in der digitalen Domain.

Dabei stehen im Grunde zwei verschiedene Prozessketten zur Verfügung: zunächst die Signalverarbeitungskette mit einer Bandbreite von ~50 MHz auf der Grundlage der extrem schnellen Hard-Real-Time-Verarbeitung mit geringem Jitter von FPGAs; die zweite Kette läuft mit einer Bandbreite von ~50 kHz über die CPU, die möglicherweise ein Hard-Real-Time-Betriebssystem (RTOS) abspielt.

DSP-Partitionierung

Eine besondere Herausforderung besteht darin, dass nahezu jedes beliebige Instrument vor der Aufgabe steht, gewaltige Eingangsdatenmengen mit groben Stichproben zu dem Ausgang des Instruments verringern zu müssen. Ein Beispiel hierfür ist ein Scope-Diagramm mit lediglich 1000 Punkten oder der Frequenzbereich-Plot eines Spektrumanalysators. Aus diesem Grund liegt die wesentliche Aufgabe der eingebetteten digitalen Signalverarbeitung in der Verringerung der Daten zwischen den Eingängen und den Ausgängen des Instruments.

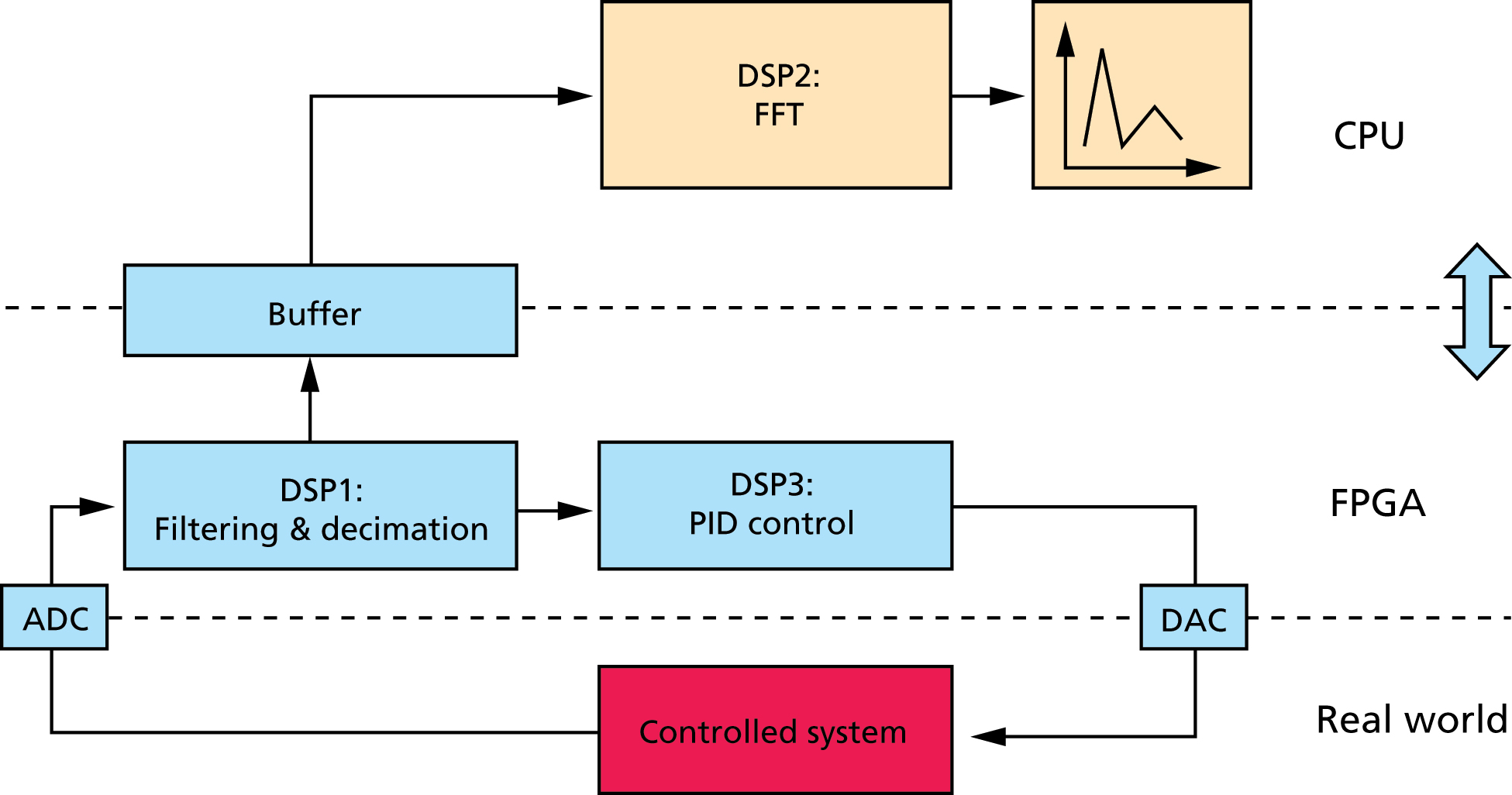

Die Kombination einer FPGA und einer CPU bietet somit deutlich mehr Möglichkeiten zur Partitionierung von Elementen der Signalverarbeitung. Ganz allgemein verarbeitet die FPGA ultra-schnelle und zugleich simple DSP-Vorgänge, wohingegen die CPU langsamere, jedoch deutlich komplexere Vorgänge des Verfahrens bearbeitet. Und trotz der erheblichen Verbesserungen von FPGA Entwicklungstools in den letzten Jahren ist es nach wie vor in aller Regel einfacher, verfahrensrelevante Software auf eine CPU auszulegen. Die zahlreichen Möglichkeiten zur Partitionierung bringen einen weiteren Vorteil ans Licht: nämlich die Möglichkeit, sehr zügig einen Prototypen eines leistungsbeschränkten jedoch vollkommen funktionierenden Systems zu erstellen. Durch die Implementierung des Großteils der DSP auf der CPU können Prototypen bereits in einer frühen Phase des Entwicklungsprojekts erstellt werden, sodass der leistungskritische Teil der DSP für ein Endprodukt mit derselben Funktion aber deutlich höherer Leistung auf die FPGA übertragen werden kann. In Abbildung 3 ist ein Beispiel der Partitionierung von DSP-Algorithmen zwischen der FPGA und der CPU dargestellt.

Abbildung 3 – Partitionierung des DSP-Algorithmus zwischen FPGA und CPU

Im Laufe der Entwicklungsarbeiten kann die Aufteilung variieren, doch ist die DSP-Verarbeitung erst einmal aufgeteilt, sind die teilweise verarbeiteten Daten von der FPGA auf die CPU oder umgekehrt zu übertragen. Die Bus-Geschwindigkeit ist dabei besonders wichtig, um zusätzliche Verzögerungen bei der Verarbeitung auszuräumen.