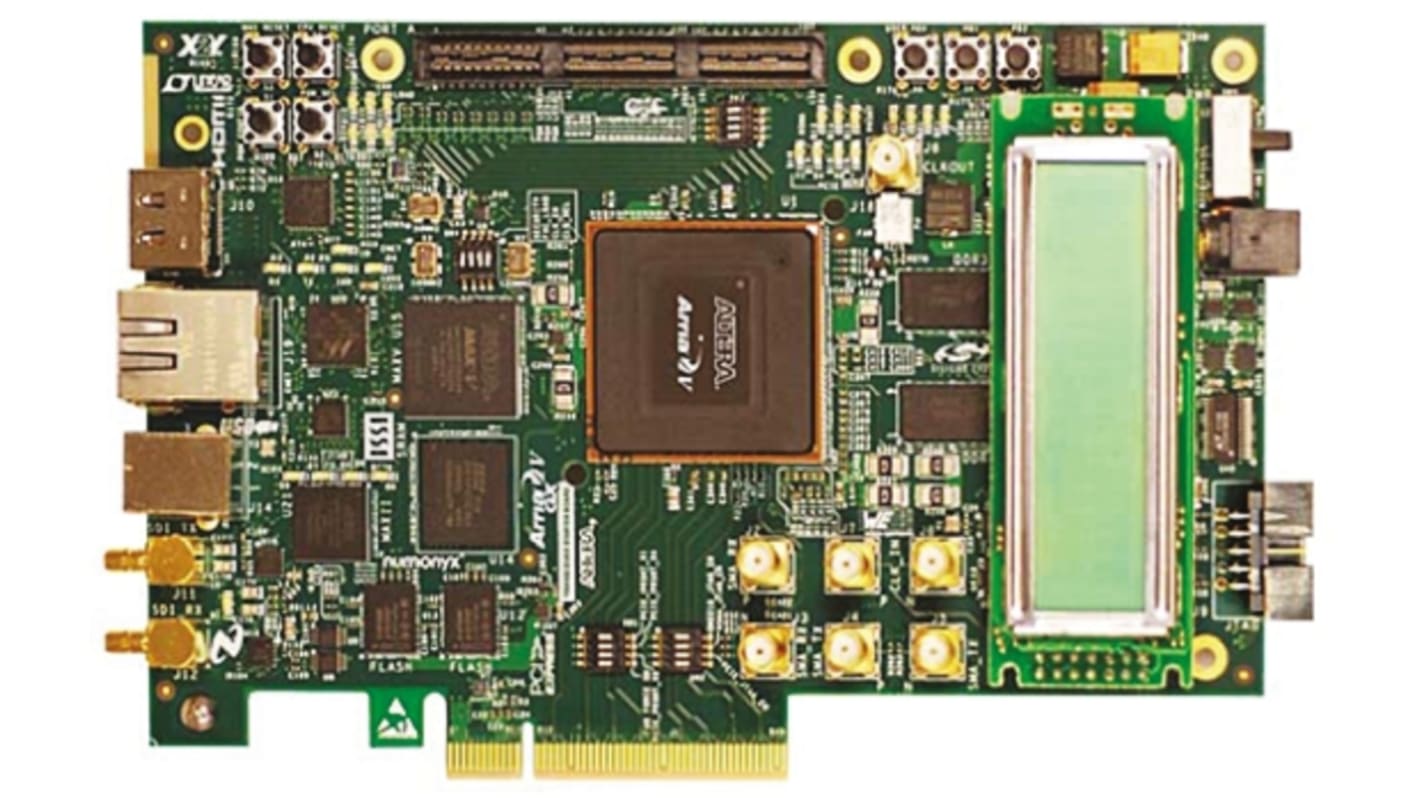

Altera Arria V GX Starterkit, FPGA, 5AGXFB3H4F35C5N

- RS Best.-Nr.:

- 787-7037

- Herst. Teile-Nr.:

- DK-START-5AGXB3N

- Marke:

- Altera

Abbildung stellvertretend für Produktreihe

Nicht verfügbar

Wir haben dieses Produkt aus dem Sortiment genommen.

- RS Best.-Nr.:

- 787-7037

- Herst. Teile-Nr.:

- DK-START-5AGXB3N

- Marke:

- Altera

Technische Daten

Mehr Infos und technische Dokumente

Rechtliche Anforderungen

Produktdetails

Finden Sie ähnliche Produkte, indem Sie ein oder mehrere Eigenschaften auswählen.

Alle auswählen | Eigenschaft | Wert |

|---|---|---|

| Marke | Altera | |

| Speicherprogrammierbare Steuerungstechnologie | FPGA | |

| Kit-Klassifizierung | Starterkit | |

| Vorgestelltes Gerät | 5AGXFB3H4F35C5N | |

| Kit-Name | Arria V GX | |

| Alle auswählen | ||

|---|---|---|

Marke Altera | ||

Speicherprogrammierbare Steuerungstechnologie FPGA | ||

Kit-Klassifizierung Starterkit | ||

Vorgestelltes Gerät 5AGXFB3H4F35C5N | ||

Kit-Name Arria V GX | ||

Starterkit Arria V GX FPGA, Altera

Das Altera Arria® V GX FPGA-Starterkit enthält die gesamte Hardware und Software zum sofortigen Entwickeln von kostenbewussten FPGA-Anwendungen. Es verfügt über Steckverbinder für eine High-Definition Multimedia Interface (HDMI) und Serial Digital Interface (SDI).

FPGA

Arria V GX 5AGXFB3H4F35C5N

Systemcontroller: MAX V-Gerät 5M2210ZF256C4N

GUI für Stromversorgungsüberwachung

Analog-Digital-Wandler (ADC) mit acht Kanälen

Nicht isolierte Stromschiene

Fast passive parallel (FPP) x16-Modus durch parallelen Flash-Loader (PFL)

Steuer- und Statusregister

Integrierter USB-Blaster II: MAX II Gerät EPM570GM100C4N

HDMI 1.3 TX

4 x XCVR, 2,7 Gbit/s (Max. durch Pegelschalter) und 270 MHz Tx-Takt, HDMI-Tx-Steckverbinder

HDMI-Pegelschalter STMicroelectronics STHDLS101T

Pegelschalter XCVR PCML 1,5 V <-> TMDS-Pegel

DDC und HPD <-> HDMI-kompatibler Pegel

Datenkanal bis 2,7 Gbit/s; kompatibel mit HDMI 1.3

Taktkanal bis 270 MHz; ausreichend, um eine Datenrate von 2,7 Gbit/s zu unterstützen

HDMI-Spezifikation: Taktperiode = 10x von UI

SDI 3G

XCVR Tx/Rx-Loopback

2 x SMB-Steckverbinder (Kabel nicht im Kit enthalten)

Bis zu 2,97 Gbit/s

Verwendet Treiber/Empfänger LMH0384SQ/LMH0303SQx von National Semiconductor

Erfordert 148,5 MHz und 148,35 MHz bei XCVR refclk zur Unterstützung der US- bzw. EU-Norm

Verwenden Sie VCXO zur Feinabstimmung und Verriegelung auf die wiederhergestellte CDR-Frequenz

HSMC

8 x XCVR bis zu 6,375 Gbit/s

Nicht konform mit PCI Express (PCIe) HIP-Anschlussbelegung

4 x CMOS

8 x Tx- und 9 x Rx-Differenzialschnittstelle mit den zugewiesenen Tx/Rx-Kanälen

2 x Takteingang Niederspannungs-Differenzialsignale (LVDS)

2 x Ausgang für Differenzialtakt

I2C-Bus

JTAG

Mindeststromunterstützung: 2 A @ 3,3 V, 1 A @ 12 V

Zugewiesener Taktbereich von Taktgeber Si 5338 für xcvr refclk

HSMC-Loopback mit BTS-GUI

SMA

XCVR Tx/Rx-Kanal

LVPECL-Takteingang

LVPECL-Taktausgang

Zugewiesener Taktbereich von Taktgeber Si 5338 für xcvr refclk

DDR3 SDRAM

Micron MT41J64M16LA-15E DDR3 SDRAM 8M x 16 x 8

Zwei Geräte: 2 x 16 Breite = x32

BTS DDR3 SDRAM-GUI mit Uniphy und Hochleistungs (HP)-Controller II

SSRAM

512K x 36, 18 MB ISSI IS61VPS51236A

Gemeinsame Adresse oder Daten mit Flash

Benutzer-E/A

LCD-Zeichendisplay

4 x DIP-Schalter

3 x Drucktaste

4 LEDs

Konfiguration

FPP x16-Modus

Dual Flash 512 Mbit Numonyx PC28F512P30BF (52 MHz fMAX)

JTAG-Stiftsockel

Integrierter USB Blaster II

Cypress-Mikrocontroller CY7C68013A als USB PHY 2.0

MAX II-Gerät

Ethernet

10 / 100 / 1000 Base-T

RJ-45-Steckverbinder, integrierte LED für Verbindungsstatus

Marvell Ethernet PHY 88E1111

Erfordert 50-MHz-Takt von CLKIN

Arria V GX 5AGXFB3H4F35C5N

Systemcontroller: MAX V-Gerät 5M2210ZF256C4N

GUI für Stromversorgungsüberwachung

Analog-Digital-Wandler (ADC) mit acht Kanälen

Nicht isolierte Stromschiene

Fast passive parallel (FPP) x16-Modus durch parallelen Flash-Loader (PFL)

Steuer- und Statusregister

Integrierter USB-Blaster II: MAX II Gerät EPM570GM100C4N

HDMI 1.3 TX

4 x XCVR, 2,7 Gbit/s (Max. durch Pegelschalter) und 270 MHz Tx-Takt, HDMI-Tx-Steckverbinder

HDMI-Pegelschalter STMicroelectronics STHDLS101T

Pegelschalter XCVR PCML 1,5 V <-> TMDS-Pegel

DDC und HPD <-> HDMI-kompatibler Pegel

Datenkanal bis 2,7 Gbit/s; kompatibel mit HDMI 1.3

Taktkanal bis 270 MHz; ausreichend, um eine Datenrate von 2,7 Gbit/s zu unterstützen

HDMI-Spezifikation: Taktperiode = 10x von UI

SDI 3G

XCVR Tx/Rx-Loopback

2 x SMB-Steckverbinder (Kabel nicht im Kit enthalten)

Bis zu 2,97 Gbit/s

Verwendet Treiber/Empfänger LMH0384SQ/LMH0303SQx von National Semiconductor

Erfordert 148,5 MHz und 148,35 MHz bei XCVR refclk zur Unterstützung der US- bzw. EU-Norm

Verwenden Sie VCXO zur Feinabstimmung und Verriegelung auf die wiederhergestellte CDR-Frequenz

HSMC

8 x XCVR bis zu 6,375 Gbit/s

Nicht konform mit PCI Express (PCIe) HIP-Anschlussbelegung

4 x CMOS

8 x Tx- und 9 x Rx-Differenzialschnittstelle mit den zugewiesenen Tx/Rx-Kanälen

2 x Takteingang Niederspannungs-Differenzialsignale (LVDS)

2 x Ausgang für Differenzialtakt

I2C-Bus

JTAG

Mindeststromunterstützung: 2 A @ 3,3 V, 1 A @ 12 V

Zugewiesener Taktbereich von Taktgeber Si 5338 für xcvr refclk

HSMC-Loopback mit BTS-GUI

SMA

XCVR Tx/Rx-Kanal

LVPECL-Takteingang

LVPECL-Taktausgang

Zugewiesener Taktbereich von Taktgeber Si 5338 für xcvr refclk

DDR3 SDRAM

Micron MT41J64M16LA-15E DDR3 SDRAM 8M x 16 x 8

Zwei Geräte: 2 x 16 Breite = x32

BTS DDR3 SDRAM-GUI mit Uniphy und Hochleistungs (HP)-Controller II

SSRAM

512K x 36, 18 MB ISSI IS61VPS51236A

Gemeinsame Adresse oder Daten mit Flash

Benutzer-E/A

LCD-Zeichendisplay

4 x DIP-Schalter

3 x Drucktaste

4 LEDs

Konfiguration

FPP x16-Modus

Dual Flash 512 Mbit Numonyx PC28F512P30BF (52 MHz fMAX)

JTAG-Stiftsockel

Integrierter USB Blaster II

Cypress-Mikrocontroller CY7C68013A als USB PHY 2.0

MAX II-Gerät

Ethernet

10 / 100 / 1000 Base-T

RJ-45-Steckverbinder, integrierte LED für Verbindungsstatus

Marvell Ethernet PHY 88E1111

Erfordert 50-MHz-Takt von CLKIN

Geliefert mit

Loopback- und Debugging-Stiftleisten-Tochterkarten, USB-Kabel, 75 Ω SMB-Videokabel, Ethernet-Kabel, Lizenz für die Development Kit Edition (DKE) der Quartus II-Software (nur Windows Plattform).

Ein FPGA ist ein Halbleitergerät, die aus einer Matrix aus konfigurierbaren Logikblöcke (CLBs) bestehen und durch programmierbare Verbindungen miteinander verbunden sind. Der Benutzer bestimmt diese Verbindungen durch die Programmierung eines SRAM. Ein CLB kann einfach (UND-, ODER-Gatter usw.) oder komplex (ein RAM-Block) sein. Der FPGA ermöglicht Designänderungen, auch nachdem das Gerät auf eine Leiterplatte gelötet wurde.