Derzeit nicht erhältlich

Wir wissen nicht, ob wir diesen Artikel noch einmal auf Lager haben werden. RS beabsichtigt, ihn bald aus dem Sortiment zu nehmen.

- RS Best.-Nr.:

- 906-3924

- Herst. Teile-Nr.:

- DK-DEV-10M50-A

- Marke:

- Altera

Technische Daten

Mehr Infos und technische Dokumente

Rechtliche Anforderungen

Produktdetails

Finden Sie ähnliche Produkte, indem Sie ein oder mehrere Eigenschaften auswählen.

Alle auswählen | Eigenschaft | Wert |

|---|---|---|

| Marke | Altera | |

| Speicherprogrammierbare Steuerungstechnologie | FPGA | |

| Kit-Klassifizierung | Development Kit | |

| Kit-Name | MAX 10 | |

| Alle auswählen | ||

|---|---|---|

Marke Altera | ||

Speicherprogrammierbare Steuerungstechnologie FPGA | ||

Kit-Klassifizierung Development Kit | ||

Kit-Name MAX 10 | ||

- Ursprungsland:

- TW

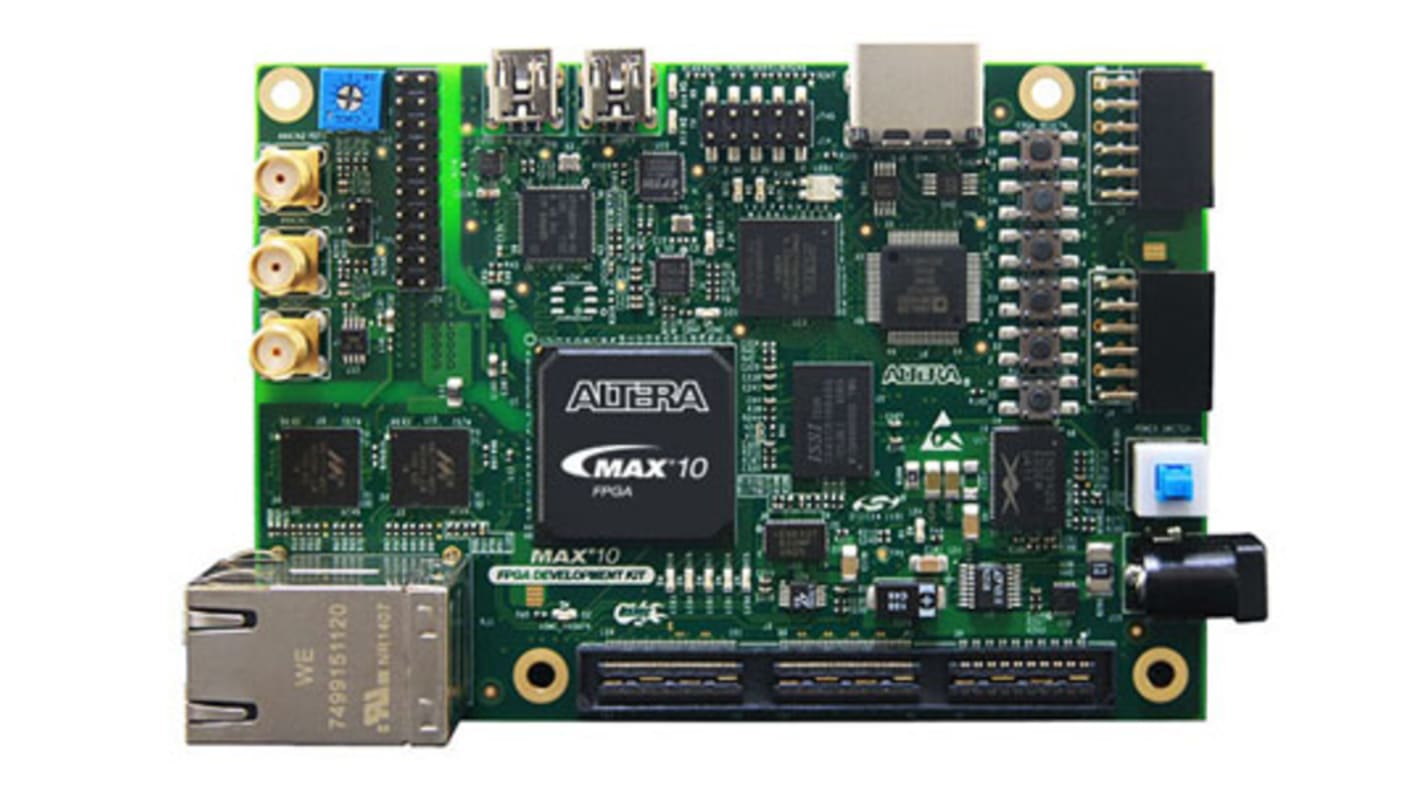

Entwicklungskit MAX 10 FPGA, Altera

Das Entwicklungskit Altera MAX 10 FPGA ist eine voll ausgestattete Designplattform, die um 50 K Logikelemente (LEs) herum entwickelt wurde. Es ist für die Integration auf Systemebene optimiert und verfügt über einen integrierten ADC, Zweifach-Konfigurations-Flash sowie eine Unterstützung von DDR3-Speicher. Es bietet eine Reihe von Konnektivitätsoptionen einschließlich eines integrierten USB-Blaster II, HDMI-Ausgangs und zweimal Ethernet für industrielle Ethernet-Anwendungen. Das Entwicklungskit MAX 10 FPGA ist eine Prototypenlösung auf Systemebene für Industrie-, Automobil- und Verbraucheranwendungen.

Mit dem Entwicklungskit Altera MAX 10 FPGA können Sie:

Mit dem Entwicklungskit Altera MAX 10 FPGA können Sie:

– Entwicklung von Designs für das FPGA 10M50D, F484-Gehäuse

– Messung der Leistungsfähigkeit der ADC-Blockumwandlung MAX 10 FPGA

– Verbindung der MAX 10 FPGAs mit DDR3-Speicher bei 300 MHz

– Betrieb von eingebettetem Linux über den Nios II-Prozessor

– Verbindung mit Tochterkarten und Peripheriegeräten über HSMC und Digilent Pmod-kompatible Steckverbinder

– Messung der FPGA-Leistung über die grafische Benutzerschnittstelle (GUI) zur Leistungsüberwachung

– Wiederverwendung der Leiterplatte und des Schaltbilds des Kits als Modell für eigene Designs

Programmierung und Konfiguration

– Integrierter USB-Blaster II (JTAG)

– Optionales JTAG direkt über 10-polige Stiftleiste

Speichergeräte

– 64-Mx16 1 GB DDR3 SDRAM mit Soft-Memory-Controller

– 128-Mx8 1 GB DDR3 SDRAM mit Soft-Memory-Controller

– 512 MB Vierfach-SPI (Serial Peripheral Interface) Flash

Kommunikationsanschlüsse

– 2 x Gigabit Ethernet RJ-45-Anschluss

– Mini-USB2.0 UART

– HDMI-Videoausgang

– Steckverbinder für Universal-Hochgeschwindigkeits-Aufsatzkarte (HSMC)

– 2 x 12-poliger Digilent Pmod-kompatibler Steckverbinder

Analog

– 2 x MAX 10 FPGA ADC SMA-Eingänge

– 2 x 10 ADC-Stiftleiste

– Potenziometereingang zu ADC

– Externer 16-bit-DAC mit SMA-Ausgang

Takt

– 25 MHz einseitige externe Oszillator-Taktquelle

– Taktgenerator Silicon Labs

Lieferumfang

– Mini-USB-Kabel für integrierten USB-Blaster II

– 2-A-Netzteil und Kabel

– Kostenlose Designsoftware Quartus II Web Edition

– Messung der Leistungsfähigkeit der ADC-Blockumwandlung MAX 10 FPGA

– Verbindung der MAX 10 FPGAs mit DDR3-Speicher bei 300 MHz

– Betrieb von eingebettetem Linux über den Nios II-Prozessor

– Verbindung mit Tochterkarten und Peripheriegeräten über HSMC und Digilent Pmod-kompatible Steckverbinder

– Messung der FPGA-Leistung über die grafische Benutzerschnittstelle (GUI) zur Leistungsüberwachung

– Wiederverwendung der Leiterplatte und des Schaltbilds des Kits als Modell für eigene Designs

Programmierung und Konfiguration

– Integrierter USB-Blaster II (JTAG)

– Optionales JTAG direkt über 10-polige Stiftleiste

Speichergeräte

– 64-Mx16 1 GB DDR3 SDRAM mit Soft-Memory-Controller

– 128-Mx8 1 GB DDR3 SDRAM mit Soft-Memory-Controller

– 512 MB Vierfach-SPI (Serial Peripheral Interface) Flash

Kommunikationsanschlüsse

– 2 x Gigabit Ethernet RJ-45-Anschluss

– Mini-USB2.0 UART

– HDMI-Videoausgang

– Steckverbinder für Universal-Hochgeschwindigkeits-Aufsatzkarte (HSMC)

– 2 x 12-poliger Digilent Pmod-kompatibler Steckverbinder

Analog

– 2 x MAX 10 FPGA ADC SMA-Eingänge

– 2 x 10 ADC-Stiftleiste

– Potenziometereingang zu ADC

– Externer 16-bit-DAC mit SMA-Ausgang

Takt

– 25 MHz einseitige externe Oszillator-Taktquelle

– Taktgenerator Silicon Labs

Lieferumfang

– Mini-USB-Kabel für integrierten USB-Blaster II

– 2-A-Netzteil und Kabel

– Kostenlose Designsoftware Quartus II Web Edition

Vorgestellte Geräte

Ein FPGA ist ein Halbleitergerät, die aus einer Matrix aus konfigurierbaren Logikblöcke (CLBs) bestehen und durch programmierbare Verbindungen miteinander verbunden sind. Der Benutzer bestimmt diese Verbindungen durch die Programmierung eines SRAM. Ein CLB kann einfach (UND-, ODER-Gatter usw.) oder komplex (ein RAM-Block) sein. Der FPGA ermöglicht Designänderungen, auch nachdem das Gerät auf eine Leiterplatte gelötet wurde.

Verwandte Links

- Altera MAX V Development Kit 5M570Z

- Altera Cyclone IV GX Development Kit, FPGA

- Altera Cyclone V Development Kit FPGA

- FTDI Chip Altera Cyclone-II Modul, FPGA

- Altera FPGA Cyclone II 4608 Zellen 4608 Einh. TQFP 144-Pin

- Altera FPGA Cyclone IV E 6272 Zellen 392 Einh. Spezieller DSP EQFP 144-Pin 270kbit

- Altera Programmiergerät USB Blaster, Cable Programming USB für FPGA

- Altera FPGA Cyclone IV GX 14400 Zellen 900 Einh. Spezieller DSP FBGA 169-Pin 14400Register 540kbit