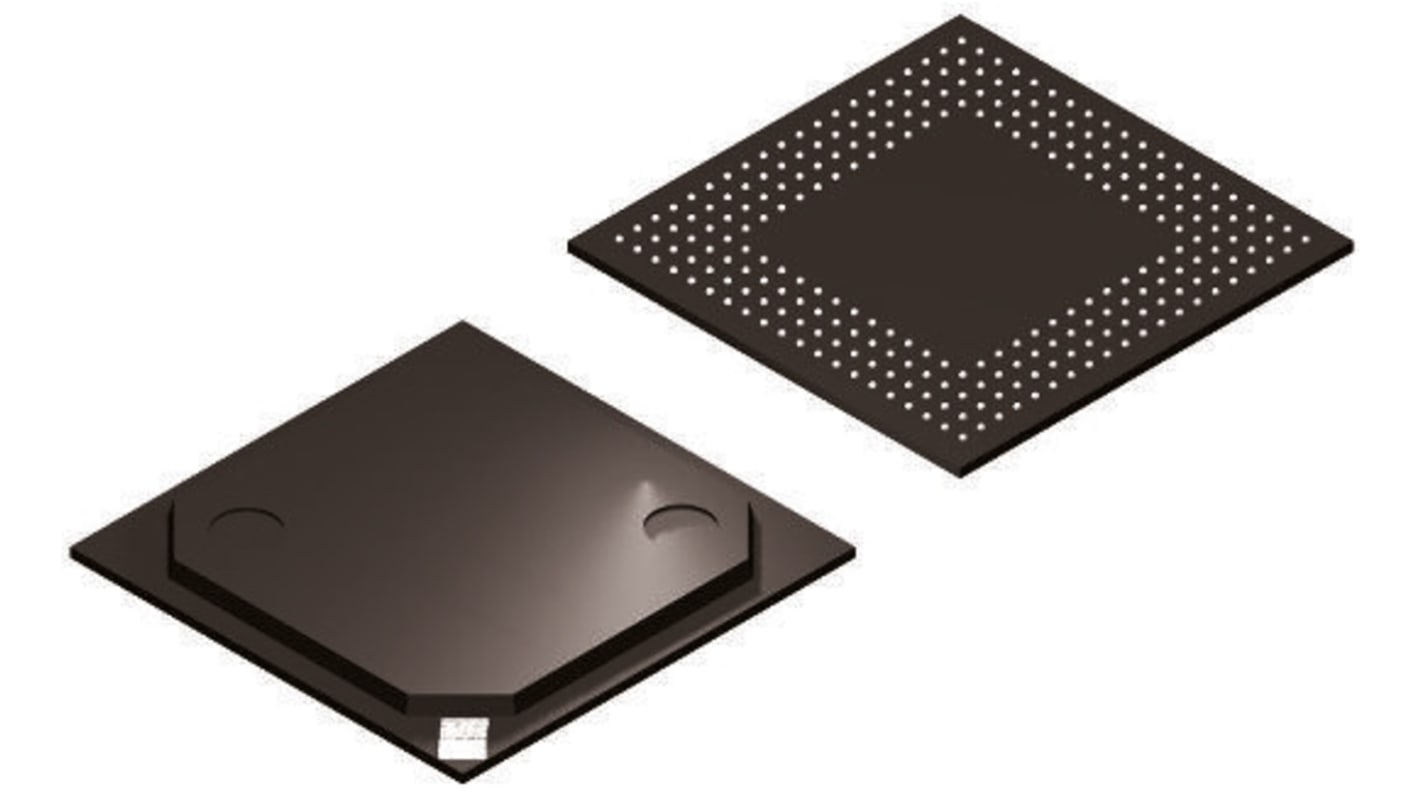

Altera FPGA 5CEBA4 49000 Gates 49000 Zellen 18480 Einh. FBGA 256-Pin 73920Register 3464192 bit

- RS Best.-Nr.:

- 830-3565P

- Herst. Teile-Nr.:

- 5CEBA4F17C8N

- Marke:

- Altera

Zwischensumme 1 Stück (geliefert in Schale)*

69,70 €

(ohne MwSt.)

82,94 €

(inkl. MwSt.)

VERSANDKOSTENFREIE Lieferung für Bestellungen ab 100,00 €

Vorübergehend ausverkauft

- Versand ab 10. Juni 2026

Sie benötigen mehr? Benötigte Menge eingeben und auf „Lieferverfügbarkeit überprüfen“ klicken.

Stück | Pro Stück |

|---|---|

| 1 + | 69,70 € |

*Richtpreis

- RS Best.-Nr.:

- 830-3565P

- Herst. Teile-Nr.:

- 5CEBA4F17C8N

- Marke:

- Altera

Technische Daten

Mehr Infos und technische Dokumente

Rechtliche Anforderungen

Produktdetails

Finden Sie ähnliche Produkte, indem Sie ein oder mehrere Eigenschaften auswählen.

Alle auswählen | Eigenschaft | Wert |

|---|---|---|

| Marke | Altera | |

| Serie | 5CEBA4 | |

| Produkt Typ | FPGA | |

| Anzahl der Logik-Gates | 49000 | |

| Anzahl der Logik-Zellen | 49000 | |

| Anzahl der Logik-Einheiten | 18480 | |

| Anzahl der Register | 73920 | |

| Anzahl der Multiplikatoren | 132 | |

| Montageart | Oberfläche | |

| Gehäusegröße | FBGA | |

| Minimale Versorgungsspannung | 1.07V | |

| Maximale Versorgungsspannung | 1.13V | |

| Pinanzahl | 256 | |

| Anzahl der RAM Bits | 3464192bit | |

| Betriebstemperatur min. | 0°C | |

| Anzahl der Ein/Ausgänge | 176 | |

| Maximale Betriebstemperatur | 85°C | |

| Breite | 17 mm | |

| Normen/Zulassungen | No | |

| Länge | 17mm | |

| Automobilstandard | Nein | |

| Alle auswählen | ||

|---|---|---|

Marke Altera | ||

Serie 5CEBA4 | ||

Produkt Typ FPGA | ||

Anzahl der Logik-Gates 49000 | ||

Anzahl der Logik-Zellen 49000 | ||

Anzahl der Logik-Einheiten 18480 | ||

Anzahl der Register 73920 | ||

Anzahl der Multiplikatoren 132 | ||

Montageart Oberfläche | ||

Gehäusegröße FBGA | ||

Minimale Versorgungsspannung 1.07V | ||

Maximale Versorgungsspannung 1.13V | ||

Pinanzahl 256 | ||

Anzahl der RAM Bits 3464192bit | ||

Betriebstemperatur min. 0°C | ||

Anzahl der Ein/Ausgänge 176 | ||

Maximale Betriebstemperatur 85°C | ||

Breite 17 mm | ||

Normen/Zulassungen No | ||

Länge 17mm | ||

Automobilstandard Nein | ||

Cyclone FPGA, Altera

Ein FPGA ist ein Halbleitergerät, die aus einer Matrix aus konfigurierbaren Logikblöcke (CLBs) bestehen und durch programmierbare Verbindungen miteinander verbunden sind. Der Benutzer bestimmt diese Verbindungen durch die Programmierung eines SRAM. Ein CLB kann einfach (UND-, ODER-Gatter usw.) oder komplex (ein RAM-Block) sein. Der FPGA ermöglicht Designänderungen, auch nachdem das Gerät auf eine Leiterplatte gelötet wurde.

Verwandte Links

- Altera FPGA Cyclone V 49000 Gates 49000 Zellen 18480 Einh. Spezieller DSP FBGA 256-Pin 73920Register 3464192

- Altera FPGA Cyclone 5980 Zellen 5980 Einh. FBGA 256-Pin

- Altera FPGA Cyclone III 15408 Zellen 15408 Einh. FBGA 484-Pin

- Altera FPGA Cyclone III 55856 Zellen 3491 Einh. Spezieller DSP FBGA 484-Pin 2396160bit

- Altera FPGA Cyclone IV 28848 Zellen 1803 Einh. FBGA 484-Pin 28848Register 594 bit

- Altera FPGA Cyclone 6272 Gates 6272 Zellen 392 Einh. Spezieller DSP FBGA 256-Pin 276480

- Altera FPGA 5CEBA2 25000 Gates 25000 Zellen 9434 Einh. FBGA 256-Pin 37736Register 2002944 bit

- Altera FPGA Cyclone II 4608 Zellen 4608 Einh. TQFP 144-Pin