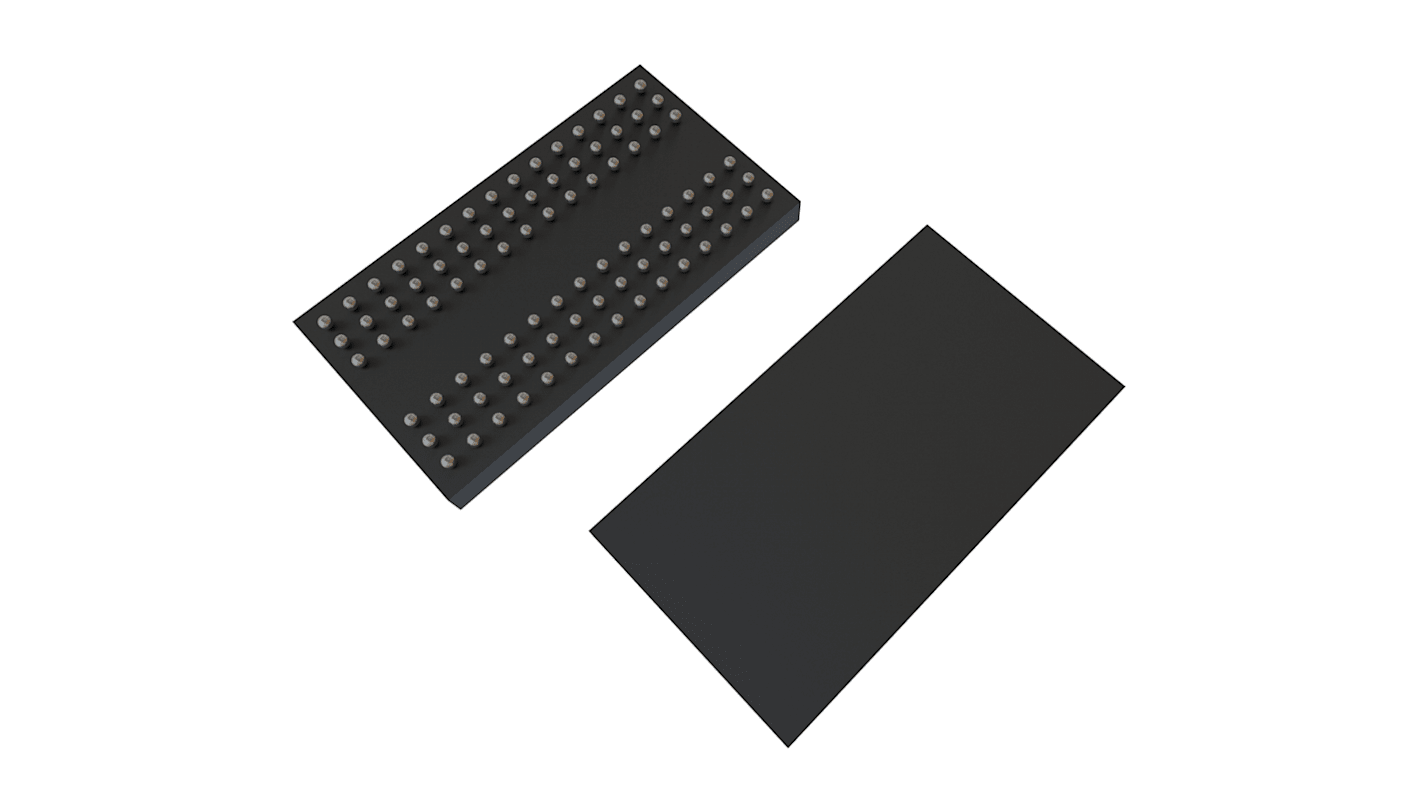

Winbond SDRAM 1Gbit 128M x 8 Bit 8bit Bits/Wort WBGA 60-Pin

- RS Best.-Nr.:

- 188-2582

- Herst. Teile-Nr.:

- W971GG8SB25I

- Marke:

- Winbond

Nicht verfügbar

Wir haben dieses Produkt aus dem Sortiment genommen.

- RS Best.-Nr.:

- 188-2582

- Herst. Teile-Nr.:

- W971GG8SB25I

- Marke:

- Winbond

Technische Daten

Mehr Infos und technische Dokumente

Rechtliche Anforderungen

Produktdetails

Finden Sie ähnliche Produkte, indem Sie ein oder mehrere Eigenschaften auswählen.

Alle auswählen | Eigenschaft | Wert |

|---|---|---|

| Marke | Winbond | |

| Speicher Größe | 1Gbit | |

| Organisation | 128M x 8 Bit | |

| Anzahl der Bits pro Wort | 8bit | |

| Anzahl der Wörter | 128M | |

| Montage-Typ | SMD | |

| Gehäusegröße | WBGA | |

| Pinanzahl | 60 | |

| Abmessungen | 12.6 x 8.1 x 0.6mm | |

| Höhe | 0.6mm | |

| Länge | 12.6mm | |

| Betriebstemperatur max. | +95 °C | |

| Arbeitsspannnung max. | 1,9 V | |

| Arbeitsspannnung min. | 1,7 V | |

| Betriebstemperatur min. | –40 °C | |

| Breite | 8.1mm | |

| Alle auswählen | ||

|---|---|---|

Marke Winbond | ||

Speicher Größe 1Gbit | ||

Organisation 128M x 8 Bit | ||

Anzahl der Bits pro Wort 8bit | ||

Anzahl der Wörter 128M | ||

Montage-Typ SMD | ||

Gehäusegröße WBGA | ||

Pinanzahl 60 | ||

Abmessungen 12.6 x 8.1 x 0.6mm | ||

Höhe 0.6mm | ||

Länge 12.6mm | ||

Betriebstemperatur max. +95 °C | ||

Arbeitsspannnung max. 1,9 V | ||

Arbeitsspannnung min. 1,7 V | ||

Betriebstemperatur min. –40 °C | ||

Breite 8.1mm | ||

Netzteil: VDD, VDDQ = 1,8 V ± 0,1 V

Doppelte Datenraten-Architektur: zwei Datenübertragungen pro Taktzyklus

CAS-Latenz: 3, 4, 5, 6 und 7

Burst-Länge: 4 und 8

Bidirektionale, differenzielle Datenströme (DQS und DQS) werden mit Daten übertragen/empfangen

Flanken-ausgerichtet beim Lesen von Daten und Mitte-ausgerichtet beim Schreiben von Daten

DLL richtet DQ- und DQS-Übergänge auf den Takt aus

Differenzielle Takteingänge (CLK und CLK)

Datenmasken (DM) für das Schreiben von Daten

Befehle, die an jeder positiven CLK-Kante, an Daten- und Datenmaske eingegeben werden, beziehen sich auf beide Kanten von DQS

Gebuchte CAS-programmierbare additive Latenz unterstützt, um die Effizienz von Befehlen und Datenbus zu steigern

Leselatenz = Additive Latenz plus CAS-Latenz (RL = AL + CL)

Off-Chip-Impedanzeinstellung des Treibers (OCD) und On-Die-Abschluss (ODT) für bessere Signalqualität

Auto-Precharge-Betrieb zum Lesen und Schreiben von Bursts

Auto-Refresh- und Self-Refresh-Modi

Precharged Abschaltung und aktive Abschaltung

Datenmaske schreiben

Schreiblatenz = Leselatenz - 1 (WL = RL - 1)

Schnittstelle: SSTL_18

Verpackt in WBGA 60-Kugel (8 x 12,5 mm2), mit bleifreien Materialien.

Doppelte Datenraten-Architektur: zwei Datenübertragungen pro Taktzyklus

CAS-Latenz: 3, 4, 5, 6 und 7

Burst-Länge: 4 und 8

Bidirektionale, differenzielle Datenströme (DQS und DQS) werden mit Daten übertragen/empfangen

Flanken-ausgerichtet beim Lesen von Daten und Mitte-ausgerichtet beim Schreiben von Daten

DLL richtet DQ- und DQS-Übergänge auf den Takt aus

Differenzielle Takteingänge (CLK und CLK)

Datenmasken (DM) für das Schreiben von Daten

Befehle, die an jeder positiven CLK-Kante, an Daten- und Datenmaske eingegeben werden, beziehen sich auf beide Kanten von DQS

Gebuchte CAS-programmierbare additive Latenz unterstützt, um die Effizienz von Befehlen und Datenbus zu steigern

Leselatenz = Additive Latenz plus CAS-Latenz (RL = AL + CL)

Off-Chip-Impedanzeinstellung des Treibers (OCD) und On-Die-Abschluss (ODT) für bessere Signalqualität

Auto-Precharge-Betrieb zum Lesen und Schreiben von Bursts

Auto-Refresh- und Self-Refresh-Modi

Precharged Abschaltung und aktive Abschaltung

Datenmaske schreiben

Schreiblatenz = Leselatenz - 1 (WL = RL - 1)

Schnittstelle: SSTL_18

Verpackt in WBGA 60-Kugel (8 x 12,5 mm2), mit bleifreien Materialien.