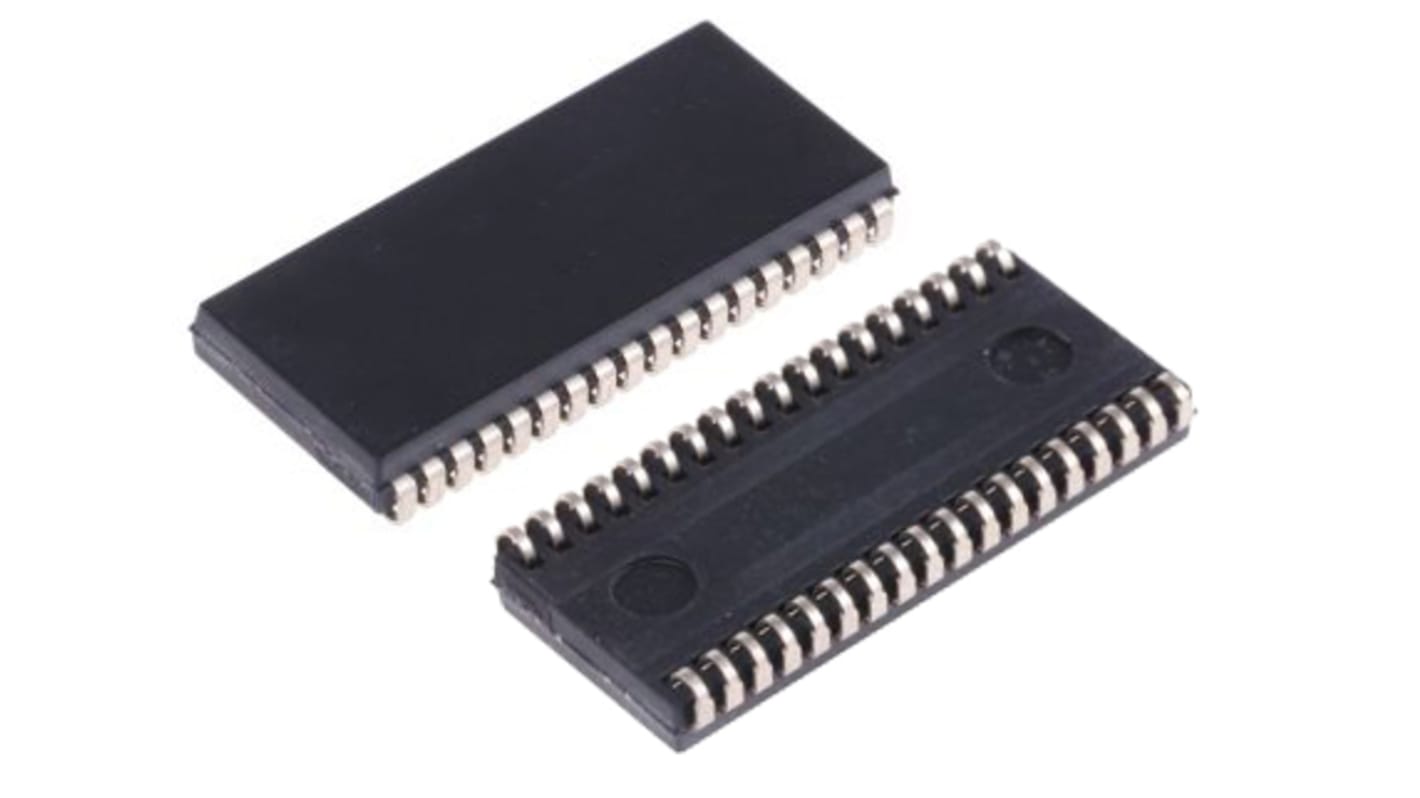

Infineon 4MBit SRAM-Speicherbaustein 512k 100MHz, 8bit / Wort 8bit, SOJ 36-Pin

- RS Best.-Nr.:

- 193-8466

- Herst. Teile-Nr.:

- CY7C1049G30-10VXI

- Marke:

- Infineon

Nicht verfügbar

Wir haben dieses Produkt aus dem Sortiment genommen.

- RS Best.-Nr.:

- 193-8466

- Herst. Teile-Nr.:

- CY7C1049G30-10VXI

- Marke:

- Infineon

Technische Daten

Mehr Infos und technische Dokumente

Rechtliche Anforderungen

Produktdetails

Finden Sie ähnliche Produkte, indem Sie ein oder mehrere Eigenschaften auswählen.

Alle auswählen | Eigenschaft | Wert |

|---|---|---|

| Marke | Infineon | |

| Speicher Größe | 4MBit | |

| Organisation | 512 k x 8 Bit | |

| Anzahl der Wörter | 512k | |

| Anzahl der Bits pro Wort | 8bit | |

| Zugriffszeit max. | 10ns | |

| Adressbusbreite | 8bit | |

| Taktfrequenz | 100MHz | |

| Timing Typ | Asymmetrisch | |

| Montage-Typ | THT | |

| Gehäusegröße | SOJ | |

| Pinanzahl | 36 | |

| Abmessungen | 0.92 x 0.395 x 0.103Zoll | |

| Arbeitsspannnung max. | 3,6 V | |

| Höhe | 2.62mm | |

| Länge | 23.37mm | |

| Betriebstemperatur max. | +85 °C | |

| Betriebstemperatur min. | –40 °C | |

| Breite | 10.03mm | |

| Arbeitsspannnung min. | 2,2 V | |

| Alle auswählen | ||

|---|---|---|

Marke Infineon | ||

Speicher Größe 4MBit | ||

Organisation 512 k x 8 Bit | ||

Anzahl der Wörter 512k | ||

Anzahl der Bits pro Wort 8bit | ||

Zugriffszeit max. 10ns | ||

Adressbusbreite 8bit | ||

Taktfrequenz 100MHz | ||

Timing Typ Asymmetrisch | ||

Montage-Typ THT | ||

Gehäusegröße SOJ | ||

Pinanzahl 36 | ||

Abmessungen 0.92 x 0.395 x 0.103Zoll | ||

Arbeitsspannnung max. 3,6 V | ||

Höhe 2.62mm | ||

Länge 23.37mm | ||

Betriebstemperatur max. +85 °C | ||

Betriebstemperatur min. –40 °C | ||

Breite 10.03mm | ||

Arbeitsspannnung min. 2,2 V | ||

CY7C1049G und CY7C1049GE sind Hochleistungs-CMOS-schnelle statische RAM-Geräte mit integriertem ECC. Beide Geräte werden in Einfach- und Zweifach-Chip-Aktivierungsoptionen und in mehreren Pinkonfigurationen angeboten. Das Gerät CY7C1049GE verfügt über einen ERR-Stift, der während eines Lesezyklus ein Fehlererkennungs- und Korrekturereignis signalisiert. Schreibvorgänge erfolgen über die Festlegung der Eingaben "Chip Enable" (CE) und "Write Enable" (WE) als NIEDRIG, und stellt die Daten gleichzeitig über E/A-0 bis E/A-7 sowie die Adresse über die Pole A-0 bis A-18 zur Verfügung. Lesevorgänge erfolgen über die Festlegung der Eingaben "Chip Enable" (CE) und "Write Enable" (WE) als NIEDRIG, unter Angabe der erforderlichen Adresse und der Adresszeilen. Daten werden über die E/A-Leitungen ausgelesen (E/A-0 bis E/A-7).

Hohe Geschwindigkeit

tAA = 10 ns

Integrierter ECC für Einzelbit-Fehlerkorrektur [1, 2]

Niedriger Wirk- und Standby-Strom

Wirkstrom: ICC = 38 mA (typisch)

Standby-Strom: ISB2 = 6 mA (typisch)

Betriebsspannungsbereich: 1,65 V bis 2,2 V, 2,2 V bis 3,6 V und 4,5 V bis 5,5 V

1,0-V-Datenspeicherung

TTL-kompatible Ein- und Ausgänge

Fehleranzeige-Stift (ERR) zeigt Erkennung und Korrektur von 1-Bit-Fehlern an

Bleifreie, 36-polige SOJ-Gehäuse sowie 44-polige TSOP-II-Gehäuse

tAA = 10 ns

Integrierter ECC für Einzelbit-Fehlerkorrektur [1, 2]

Niedriger Wirk- und Standby-Strom

Wirkstrom: ICC = 38 mA (typisch)

Standby-Strom: ISB2 = 6 mA (typisch)

Betriebsspannungsbereich: 1,65 V bis 2,2 V, 2,2 V bis 3,6 V und 4,5 V bis 5,5 V

1,0-V-Datenspeicherung

TTL-kompatible Ein- und Ausgänge

Fehleranzeige-Stift (ERR) zeigt Erkennung und Korrektur von 1-Bit-Fehlern an

Bleifreie, 36-polige SOJ-Gehäuse sowie 44-polige TSOP-II-Gehäuse

Verwandte Links

- Infineon 4MBit SRAM-Speicherbaustein 512k 100MHz SOJ 36-Pin

- Renesas Electronics 4MBit SRAM 512K 1MHz SOJ 36-Pin

- Infineon 1MBit SRAM-Speicherbaustein 128k 1MHz SOJ 32-Pin

- Cypress Semiconductor 4MBit SRAM-Speicherbaustein 256k, 16bit / Wort

- Infineon 1MBit LowPower SRAM 128k SOJ 32-Pin

- Infineon 4 MB SRAM 512K SOJ 36-Pin

- Alliance Memory 4MBit LowPower SRAM 512k TSOP 32-Pin

- Infineon 4 MB SRAM 512K 100 MHz 36-polig gegossen SOJ/44-polig TSOP II 44-Pin